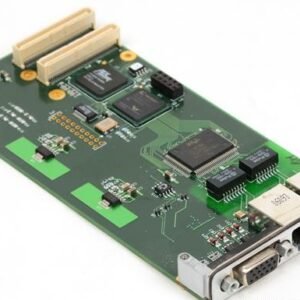

The Acromag IP-1K100-0024 is a user-programmable FPGA module built around the Altera EP1K100 device for embedded custom logic implementation and high-speed data processing. This Industry Pack (IP) module enables adaptive computing through in-system FPGA configuration via JTAG or IP bus, with a pre-programmed CPLD handling power-up initialization. Engineers develop applications in VHDL using Altera MAX+PLUS® II or Quartus® tools, downloading directly to the FPGA through the IP bus.

Technical Specifications

• FPGA Device: Altera EP1K100

• Configuration Interface: JTAG or IP bus with internal CPLD-facilitated initialization

• Digital I/O Capacity: Up to 48 TTL or 24 EIA-485 signals, or mixed configuration

• TTL I/O: 5V tolerant; grouped directional control in 8-channel sets

• Differential I/O: RS485/RS422 transceivers; grouped control in 4-channel sets

• RS485/RS422 Range: Up to 32 nodes over 4000 feet of cable

• IP Bus Clock: 8 MHz and 32 MHz operation

• IP Bus Standard: ANSI/VITA 4-1995 compliant

• ID Space Read Access (8 MHz): 0 wait states, 250 ns cycle time

• Register Read/Write Access (8 MHz): 1 wait state, 500 ns cycle time

• Data Widths: 8-bit ID space; 8 or 16-bit I/O space

• Interrupt Support: Two IP request levels

• Clock Synthesizer: PLL-based, programmable 250 kHz to 100 MHz output

• External Clock Input: LVTTL with direct FPGA global clock connection

• Interval Timer: User-programmable

• Power Input: 12 V to 32 V DC with reverse-polarity protection

• Operating Temperature: −40°C to +60°C ambient

– Key Features

• In-system reprogrammable logic via standard JTAG interface

• Flexible I/O mixing of TTL and differential signals

• Wide-range DC power input with reverse-polarity protection

• Programmable clock synthesis from 250 kHz to 100 MHz

• Support for specialized EIA-422/485 communication networks

• Extended temperature operation from −40°C to +60°C

– Typical Applications

• Specialized communication systems over EIA-422/485 networks

• Signal simulation over TTL-switched lines

• Advanced data analysis and custom signal processing

• Adaptive computing requiring field-programmable logic

– Compatibility & Integration

The module conforms to ANSI/VITA 4-1995 IP bus specifications and integrates with standard FPGA design flows. DMA is wired to the FPGA but not supported in the provided example firmware.