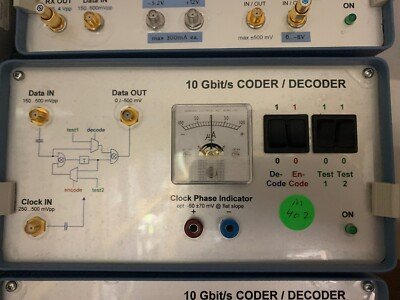

The CDR Coder/Decoder is a deserializer module with integrated clock recovery, engineered for high-speed serial-to-parallel conversion at 9.953 Gbit/s and 10.3125 Gbit/s. It accepts CML differential serial data, performs bit-error detection, and outputs 16-bit parallel LVDS data with precise clock alignment. Built for SONET/SDH and 10 Gbps Ethernet validation, it provides Loss-of-Lock and Sync-Error indicators, clock holdover capability, and supports multiple PRBS test patterns for comprehensive signal diagnostics.

Technical Specifications

• Data Rate: 9.953 Gbit/s / 10.3125 Gbit/s

• Serial Input: CML differential, 100 mV p-p to 1.2 V p-p

• Parallel Output: 16-bit LVDS

• Jitter Tolerance: 0.75 UI p-p (0.50 UI deterministic + 0.25 UI random)

• Reference Clock: Baud Rate/64 or Baud Rate/16

• Output Clock Delay: −150 ps to +150 ps

• Clock Duty Cycle: 45% to 55%

• Power Supply: +3.0 V to +3.6 V (nominal +3.3 V)

• Power Dissipation: Typically 1.5 W

• Operating Temperature: 0°C to +85°C

• Package: 68-pin QFN (10 mm × 10 mm)

– Key Features

• TTL-compatible Loss-of-Lock and Sync-Error status indicators

• Clock holdover function maintains reference clock during data loss

• Support for PRBS patterns: 2^31-1, 2^23-1, 2^20-1, 2^15-1, 2^11-1, 2^9-1, 2^7-1, and QRSS

• Loss-of-Signal (LOS) detection via TTL input

• Low jitter clock recovery with wide input amplitude range

– Typical Applications

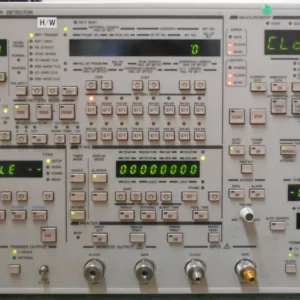

• OC-192 SONET/SDH signal validation and diagnostics

• 10 Gbps Ethernet LAN/WAN testing

• Add/Drop Multiplexer (ADM) tributary mapping and de-mapping

• Digital Cross-Connect (DXC) signal integrity verification

• Bit Error Rate (BERT) testing in out-of-service environments

• High-speed telecom infrastructure error analysis

– Compatibility & Integration

Designed for OC-192 SONET/SDH and 10 Gbps Ethernet standards. Single +3.3 V supply operation with low power dissipation enables integration into compact test and measurement systems.