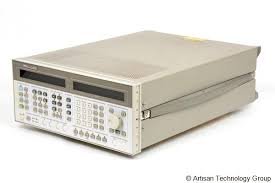

The Stanford Research Systems CG644 is a programmable PECL clock generator delivering stable, low-jitter signals up to 2050 MHz. Built on the proven CG635 Synthesized Clock Generator platform, it combines precise frequency control with fast transition times and exceptional timebase stability, making it ideal for high-speed digital system synchronization, test automation, and laboratory signal generation.

Technical Specifications

• Frequency Range: DC to 2050 MHz

• Output Type: PECL (+3.3Vcc)

• Jitter (rms): <1 ps rms

• Transition Time (Rise/Fall): Typically 80 ps (20% to 80%)

• Frequency Resolution: 16 digits

• Output Impedance: 50 Ω (front-panel outputs); 100 Ω differential (rear-panel outputs)

• Load Impedance: 50 Ω (front-panel); 100 Ω differential (rear-panel)

• Timebase Stability: Better than 5 ppm (crystal standard); optional OCXO and Rubidium timebases available

• Power Supply: +3.3Vcc for PECL outputs; universal AC input worldwide; +5 V and -5 V accessory power on rear panel

– Key Features

• Complementary Q and -Q front-panel outputs for differential signaling

• Rear-panel RJ-45 connector supporting LVDS differential outputs to 2.05 GHz and RS-485 levels to 105 MHz

• CAT-6 cable compatible with 100 Ω terminations

• 10 MHz reference input and output

• Phase and time modulation inputs

• GPIB and RS-232 remote control interfaces

– Typical Applications

• High-speed digital system clocking and synchronization

• Test and measurement equipment timing

• Data acquisition system synchronization

• RF and microwave instrumentation

• Laboratory clock generation

– Compatibility & Integration

The CG644 integrates with standard 50 Ω and 100 Ω differential test infrastructure. Remote programming via GPIB or RS-232 enables seamless automation in ATE and laboratory environments. Optional precision timebases extend stability for demanding metrology applications.