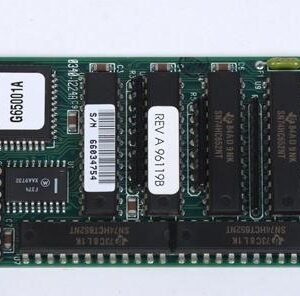

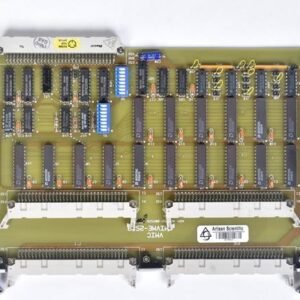

The Abaco Systems IP-Altera-TTL and IP-Altera-TTL-RO are single-wide IndustryPack modules that deliver TTL digital I/O interfacing built around an Altera 10K40-3 FPGA. These modules provide 28 total digital I/O lines—20 differential and 8 TTL—with fully programmable line direction and tri-state capability. Purpose-built for non-standard communication protocols in aerospace and satellite test environments, they enable custom digital interface implementation without external glue logic.

Technical Specifications

• FPGA Core: Altera 10K40-3

• Total Digital I/O: 28 lines (20 differential + 8 TTL)

• Reference Output: 1.5 V available on dedicated I/O pin

• IndustryPack Bus: 32 MHz IP Specification with 1 wait state

• Form Factor: Single-wide IndustryPack

– Key Features

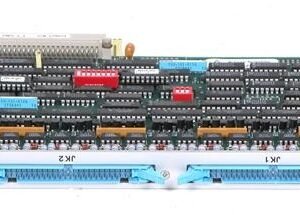

• Each I/O line direction is independently programmable

• TTL lines integrate LineSafe ESD protection

• TTL outputs support tri-state buffering

• Differential lines feature separate output enable bits and socketed termination resistors

• 1.5 V reference output enables differential receivers to function as TTL inputs when reference is connected to receiver minus input

• Supplied Altera design file-set (version 7.1) includes basic schematic, ACF file, simulation files, vector files, IndustryPack bus control interface, digital I/O examples, interrupt implementation, and ID PROM configuration

– Typical Applications

Satellite and aerospace test systems requiring non-standard protocol support. Instrumentation platforms where custom digital interface logic cannot be accommodated on the host carrier card. Systems needing flexible TTL and differential I/O mixing on a single module.

– Compatibility & Integration

Requires external Altera Development System for custom design implementation. Operates with any IndustryPack-compatible carrier supporting the 32 MHz IP Specification.