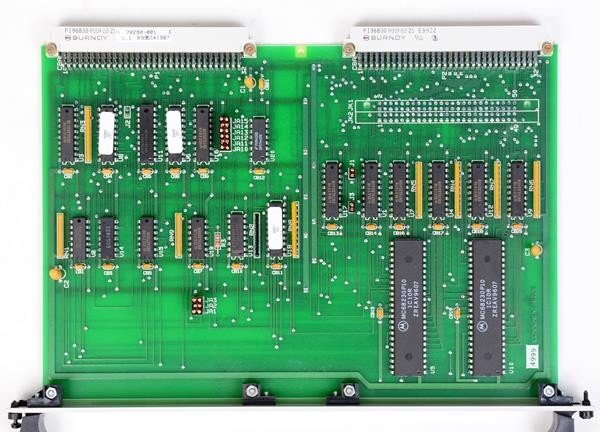

The XVME-290 is a 32-channel TTL I/O module for VMEbus systems, delivering digital signal interfacing across four independently configurable 8-bit ports. Built on two 68230 Parallel Interface/Timer devices, this 6U double-height board routes all I/O through the VMEbus P2 connector and includes buffered inputs/outputs, VMEbus interrupt capability, and dual 24-bit timers for precise timing control in industrial automation, data acquisition, and process control applications.

Technical Specifications

Digital I/O Architecture

• 32 TTL-level channels across four software-selectable 8-bit ports

• Two 68230 PI/T interface devices with buffered I/O

• Two 24-bit timer devices

• VMEbus interrupt capable with configurable interrupt levels

• Handshaking support

Electrical Characteristics

• Input logic thresholds: 0.8 V (maximum), 2.0 V (minimum)

• Output: 0.4 V @ 12 mA (maximum), 2.4 V @ -3 mA (minimum)

• Supply: +5 V

• Power consumption: 1.3 A typical, 1.5 A maximum

Physical & Environmental

• 6U double-height form factor: 160 mm × 233.4 mm

• I/O via VMEbus P2 connector

• Operating temperature: 0 °C to 32 °C

• Storage temperature: -40 °C to 85 °C

• Humidity: 5% to 95% RH (non-condensing)

• Operating altitude: 0 to 10,000 ft

• Vibration: 5–2,000 Hz, 0.015 in peak-to-peak, 2.5 g peak acceleration

• Shock: 30 g operating

– Key Features

• Four independent 8-bit ports with software-selectable directionality

• Dual 24-bit timers for timing and counting operations

• Hot-swappable module design

• Configurable base address, address modifier, and interrupt settings via jumpers

• VMEbus-compliant architecture

– Typical Applications

Industrial automation control, real-time data acquisition systems, process control interfaces, and distributed I/O subsystems requiring reliable TTL-level digital signal routing in VME-based platforms.

– Compatibility & Integration

Fully VMEbus-compliant for integration with mainstream VME systems. Pin-compatible with OPTO 22-style signal conditioning equipment. Multiple jumper configurations support flexible system integration and addressing schemes.