The Agilent/Keysight 16821A is a 34-channel portable logic analyzer with integrated 48-channel pattern generation, purpose-built for digital system debugging and validation. The instrument combines state and timing analysis modes in a single platform, with a 15-inch color display (touch screen optional) and configurable acquisition memory up to 32 M. Adjustable signal thresholds from -5 V to 5 V in 10 mV increments enable precise single-ended measurements across high-speed buses.

Technical Specifications

Logic Analyzer

• 34 channels with up to 32 M acquisition memory (selectable: 1 M, 4 M, 16 M, 32 M)

• Threshold adjustment: -5 V to 5 V in 10 mV increments

• 15-inch color display with optional touch screen

Timing Analysis (Asynchronous)

• Timing zoom resolution: 4 GHz (250 ps) with 64 K memory

• Conventional timing: 1.0 GHz / 500 MHz (half / full-channel) with deep memory

• Transitional timing: 500 MHz

State Analysis (Synchronous)

• State clock rates: up to 250 MHz

• Data rates: up to 250 Mb/s

• Automated threshold and sample position setup for high-speed buses

• Simultaneous eye diagrams on all channels

Pattern Generator

• 48 channels at up to 300 MVector/s vector speed

• 16 M vector depth

• Multiple logic level support: 5 V TTL, 3-state TTL, 3-state TTL/CMOS, 3-state 1.8 V, 3-state 2.5 V, 3-state 3.3 V, ECL, 5 V PECL, 3.3 V LVPECL, LVDS

• Clock pod: internal programmable 1 MHz to 300 MHz, external DC to 300 MHz, 7 ns output delay in 14 steps

• Clock input minimum high time: 1.3 ns

– Key Features

• Dual analysis capability: state and timing modes in single session

• Component substitution via pattern generation for functional testing

• 3-bit pattern level sensing on clock pod data inputs

• 10/100 Base-T LAN connectivity

– Compatibility & Integration

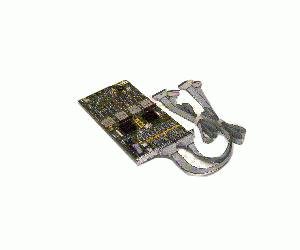

The 16821A is part of the 16800 Series and accepts 40-pin logic analyzer probes (ordered separately). Clock and data pods are field-installable and ordered separately. Memory depth in 250 Mb/s state mode is reduced by half when all pods are assigned; full depth available with one pod pair unassigned.