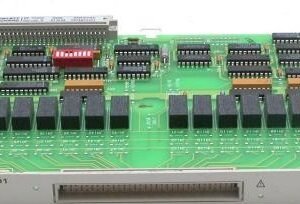

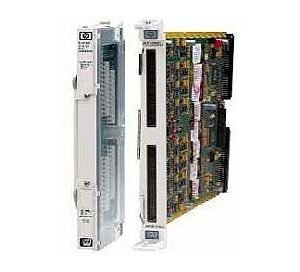

The Astronics/EADS/Racal 1260-14 is a 96-line digital I/O module for high-density interfacing in industrial and aerospace test systems. This single-slot, C-size VXIbus module delivers twelve independently configurable 8-bit ports with TTL, CMOS, or Open Collector logic level support. Each channel configures independently as input or output, enabling flexible signal routing for data acquisition and control applications. The module operates in asynchronous, synchronous, or mixed modes, with optional two-wire programmable handshaking for managed I/O transactions. Data representation options include hex, decimal, and binary formats.

## Technical Specifications

• **Channels:** 96 total, organized as twelve 8-bit ports

• **Logic Levels:** TTL compatible, CMOS compatible, Open Collector (OC)

• **Output Voltage (TTL):** Vout (high) ≥ 2.4 V @ –15 mA

• **Output Voltage (CMOS):** Vout (high) ≥ 3.8 V @ 6 mA

• **Output Voltage (Open Collector):** 5 V to 32 V

• **Input Resistance:** > 500 kΩ

• **Current Sink (OC):** Up to 200 mA per channel

• **External Pull-up Supply (OC):** Up to 32 VDC; 1 A maximum per Vext pin

• **Interface:** Message-based (Option 01) or message-based + register-based (Option 01T)

• **Form Factor:** Single-slot, C-size, message-based VXIbus module

## Key Features

• Per-group internal or external pull-up selection for Open Collector outputs

• Programmable handshake control—each line configurable as active high or active low

• Pseudo tri-state output capability via software control (1260-14C)

• Suitable for driving external circuitry, switches, relays, and digital logic devices

• Inductive load applications require external voltage supply to protect output stage

## Typical Applications

• Industrial equipment control and monitoring

• Aerospace test and diagnostic systems

• Switch and relay control networks

• Multi-channel data acquisition and signal routing

• Mixed-signal test benches with synchronous timing requirements

## Compatibility & Integration

The 1260-14 integrates into VXIbus systems via message-based or hybrid message/register-based command architectures. Configurable logic levels enable interfacing with legacy TTL equipment, modern CMOS systems, and high-voltage Open Collector circuits operating up to 32 VDC.