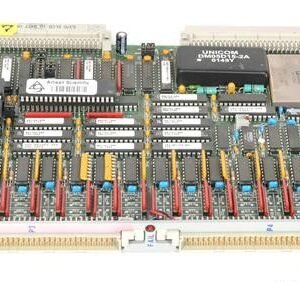

The Active Silicon Phoenix-D36-PE1 is a PCI Express digital frame grabber designed for high-speed image acquisition in industrial, medical, and scientific applications. It captures digital data from frame and line scan cameras via LVDS and RS-422 interfaces, delivering burst rates exceeding 190 MBytes/sec over a single-lane PCIe v1.1 connection. The board employs an FPGA for flexible, software-configurable interfacing and includes hardware-accelerated DataMapper for real-time reformatting of camera data.

Technical Specifications

• Data Interface: 36-bit EIA-644 (LVDS) inputs plus 4 dedicated control bits (Frame Enable, Line Enable, Data Enable, Pixel Clock)

• Pixel Clock: Maximum 60 MHz

• Data Width Support: Single 12-bit RGB or 32-bit mono; multi-tap configurations; alternative mode supports two independent 16-bit mono cameras

• Mono Data Widths: 8-, 10-, 12-, 14-, 16-, or 32-bit

• Color Data Widths: 15-, 16-, 24-, 32-, or 48-bit RGB/BGR

• Camera Tap Formats: Line interlaced, line offset, pixel interlaced, pixel offset

• PCI Express: Single-lane (x1) v1.1; burst rates exceed 190 MBytes/sec

• Bus Mastering: 0% CPU utilization for scatter-gather operations

• Power Consumption: +3.3V at 1A typical

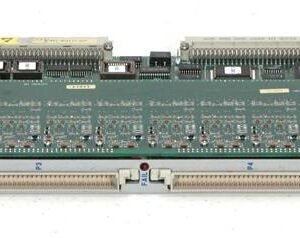

– Key Features

• Hardware DataMapper converts raw camera data on-card, including mono-to-32-bit color conversion

• Region of Interest (ROI) and sub-sampling controls optimize processing speed

• Dual UART channels support EIA-232 (RS-232) and EIA-644 (LVDS) signaling

• 4-bit opto-isolated I/O with configurable input/output allocation; outputs sink 20 mA from 24V; inputs sense 3.3V to 24V as logic high

• Two 2-bit differential LVDS input ports (AuxInXY) for external devices such as shaft encoders

• Two 8-bit TTL I/O ports

• FPGA-based 16-bit input, 16-bit lookup table (LUT) for custom processing

– Typical Applications

Machine vision, automated inspection, medical imaging, scientific research, and industrial quality control requiring flexible multi-camera acquisition and on-board data conditioning.

– Compatibility & Integration

Supports multi-tap and single-tap camera architectures with line and pixel interlacing. Compatible with standard frame and line scan cameras using LVDS control and data signaling. End-of-life product; contact sales for alternative solutions.