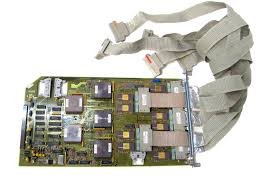

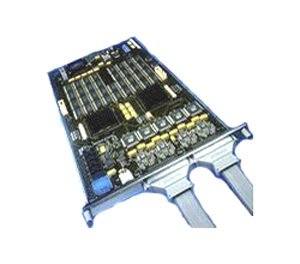

The Agilent/Keysight 16510B is an 80-channel logic analyzer module designed to expand the Agilent/Keysight 16500A mainframe with dual-mode state and timing analysis for digital circuit debugging and verification. State analysis operates at up to 35 MHz with 1024 samples per channel and 60 ns minimum state intervals. Timing analysis reaches 100 MHz with 5 ns glitch detection and transitional timing mode that extends memory to 5000 seconds at 10 ns resolution. The module supports asynchronous pattern triggering, glitch/edge detection, and five independent clock inputs with four qualifiers. Five input pods accommodate passive probes requiring 600 mVp-p minimum swing, with individually configurable thresholds from −9.9 V to +9.9 V in 0.1 V increments and dynamic range of ±10 V about threshold. Time correlation and simultaneous state/state or state/timing analysis operate across the 16500A intermodule bus. Preprocessor adapters enable direct microprocessor support for Intel, Motorola, Zilog, National, Hitachi, GTE, Rockwell, and NEC architectures, with software conversion of state data to mnemonics.

Technical Specifications

• Channels: 80

• State Analysis: 35 MHz max clock rate, 1024 samples per channel, 60 ns minimum state interval, 20 ns setup time, 5 ns hold time

• Timing Analysis: 100 MHz max clock rate, 5 ns minimum detectable glitch, 20 ns to 50 ms sample period, 512 samples per channel

• Transitional Timing Mode: 10 ns sample period, covers 10.24 µs to 5000 seconds

• Memory: 1 KB base; extended via transitional timing

• Threshold Range: −9.9 V to +9.9 V in 0.1 V increments; TTL preset +1.6 V, ECL preset −1.3 V

• Maximum Input Voltage: ±40 V peak

• Dynamic Range: ±10 V about threshold

• Probe Input: 100 kΩ ±2% impedance with ~8 pF; 600 mVp-p minimum swing; 250 mV or 30% overdrive minimum

• Clock Inputs: 5 available with 4 qualifiers

– Key Features

• Asynchronous pattern triggering based on duration

• Glitch/edge triggering with continuous pattern detection

• Dual-mode analysis: simultaneous state/state or state/timing

• Time tagging for transition duration measurement

• Pod-by-pod threshold configuration (pods 1–3 individual; pods 4–5 shared)

• Time correlation over 16500A intermodule bus

– Microprocessor Support

CPU-socket preprocessor adapters for Intel, Motorola, Zilog, National, Hitachi, GTE, Rockwell, and NEC families with mnemonic conversion software.

– Compatibility & Integration

Expands Agilent/Keysight 16500A mainframe with multimodule synchronization and data correlation.